# Z8000 MICROPROCESSOR FAMILY

# PROGRAMMING

1<sup>st</sup> EDITION

# Z8000 MICROPROCESSOR FAMILY

**PROGRAMMING**

**1st EDITION**

### **JUNE 1990**

# CONTENTS

| Instruction Set                            | 1   |

|--------------------------------------------|-----|

| Introduction                               | 1   |

| Functional Summary                         | 1   |

| Load and Exchange Instructions             | 1   |

| Arithmetic Instructions                    | 2   |

| Logical Instructions                       | 3   |

| Program Control Instructions               | 3   |

| Bit Manipulation Instructions              | 4   |

| Rotate and Shift Instructions              | 5   |

| Block Transfer And String Manipulation     | 5   |

| Input/Output Instructions                  | 6   |

| CPU Control Instructions                   | 7   |

| Extended Instructions                      | 7   |

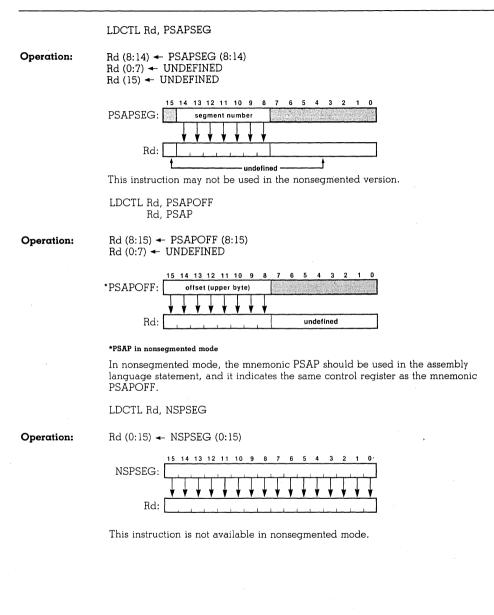

| Processor Flags                            | 8   |

| Condition Codes                            | 9   |

| Instruction Interrupts and Traps           | 9   |

| Notation and Binary Encoding               | 10  |

| Z8000 Instruction Descriptions and Formats | 13  |

| EPA Instruction Templates                  | 169 |

| Programmers Quick Reference                |     |

# Instruction Set

#### Introduction

This Manual describes the instruction set of the Z8000. An overview of the instructions are divided into ten functional groups. The instructions in each group are listed, followed by a summary description of the instructions. Significant characteristics shared by the instructions in the group, such as the available addressing modes, flags affected, or interruptibility, are described. Unusual instructions or features that are not typical of predecessor microprocessors are pointed out.

Following the functional summary of the instruction set, flags and condition codes are

discussed in relation to the instruction set. This is followed by a section discussing interruptibility of instructions and a description of traps. The last part of this chapter consists of a detailed description of each Z8000 instruction, listed in alphabetical order. This section is intended to be used as a reference by Z8000 programmers. The entry for each instruction includes a description of the instruction, addressing modes, assembly language mnemonics, instruction formats, execution times and simple examples illustrating the use of the instruction.

#### **Functional Summary**

This section presents an overview of the Z8000 instructions. For this purpose, the instructions may be divided into ten functional groups:

- Load and Exchange

- Arithmetic

- Logical

- Program Control

- Bit Manipulation

- Rotate and Shift

- Block Transfer and String Manipulation

- Input/Output

- CPU Control

- Extended Instructions

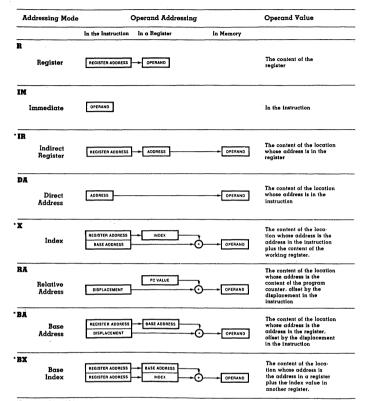

The Load and Exchange group includes a variety of instructions that provide for movement of data between registers, memory, and the program itself (i.e., immediate data). These instructions are supported with the widest range of addressing modes, including the Base (BA) and the Base Index (BX) mode which are available here only. None of these instructions affect any of the CPU flags.

The Load and Load Relative instructions transfer a byte, word, or long word of data from the source operand to the destination operand. A special one-word instruction, LDK, is also included to handle the frequent requirement for loading a small constant (0 to 15) into a register.

#### Load and Exchange Instructions.

| Instruction         | Operand(s)    | Name of Instruction   |

|---------------------|---------------|-----------------------|

| CLR<br>CLRB         | dst           | Clear                 |

| EX<br>EXB           | dst, src      | Exchange              |

| LD<br>LDB<br>LDL    | dst, src      | Load                  |

| LDA                 | dst, src      | Load Address          |

| LDAR                | dst, src      | Load Address Relative |

| LDK                 | dst, src      | Load Constant         |

| LDM                 | dst, src, num | Load Multiple         |

| LDR<br>LDRB<br>LDRL | dst, src      | Load Relative         |

| POP.<br>POPL        | dst, src      | Рор                   |

| PUSH<br>PUSHL       | dst, src      | Push                  |

These instructions basically provide one of the following three functions:

Load a register with data from a register or a memory location.

1

- Load a memory location with data from a register.

- Load a register or a memory location with immediate data.

The memory location is specified using any of the addressing modes (IR, DA, X, BA, BX, RA).

The Clear and Clear Byte instructions can be used to clear a register or memory location to zero. While this is functionally equivalent to a Load Immediate where the immediate data is zero, this operation occurs frequently enough to justify a special instruction that is more compact and faster.

The Exchange instructions swap the contents of the source and destination operands.

The Load Multiple instruction provides for efficient saving and restoring of registers. This can significantly lower the overhead of procedure calls and context switches such as those that occur at interrupts. The instruction allows any contiguous group of 1 to 16 registers to be transferred to or from a memory area, which can be designated using the DA, IR or X addressing modes. (R0 is considered to follow R15, e.g., one may save R9-R15 and R0-R3 with a single instruction.)

Stack operations are supported by the PUSH, PUSHL, POP, and POPL instructions. Any general-purpose register (or register pair in segmented mode) may be used as the stack pointer except R0 and RR0. The source operand for the Push instructions and the destination operand for the Pop instructions may be a register or a memory location. specified by the DA, IR, or X addressing modes. Immediate data can also be pushed onto a stack one word at a time. Note that byte operations are not supported, and the stack pointer register must contain an even value when a stack instruction is executed. This is consistent with the general restriction of using even addresses for word and long word accesses.

The Load Address and Load Address Relative instructions compute the effective address for the DA, X, BA, BX and RA modes and return the value in a register. They are useful for management of complex data structures.

The Arithmetic group consists of instructions for performing integer arithmetic. The basic instructions use standard two's complement binary format and operations. Support is also provided for implementation of BCD arithmetic.

| Arithmetic<br>Instruction | Instructions<br>Operand(s) | Name of Instruction |

|---------------------------|----------------------------|---------------------|

| ADC<br>ADCB               | dst, src                   | Add with Carry      |

| ADD<br>ADDB<br>ADDL       | dst, src                   | Add                 |

| CP<br>CPB<br>CPL          | dst, src                   | Compare             |

| DAB                       | dst                        | Decimal Adjust      |

| DEC<br>DECB               | dst, src                   | Decrement           |

| DIV<br>DIVL               | dst, src                   | Divide              |

| EXTS<br>EXTSB<br>EXTSL    | dst                        | Extend Sign         |

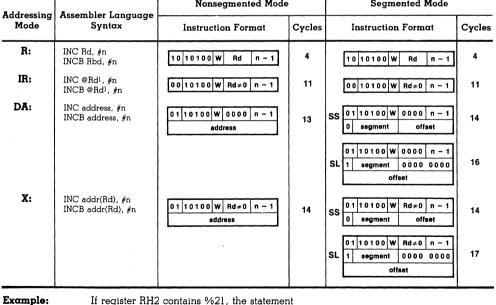

| INC<br>INCB               | dst, src                   | Increment           |

| MULT<br>MULTL             | dst, src                   | Multiply            |

| NEG<br>NEGB               | dst                        | Negate              |

| SBC<br>SBCB               | dst, src                   | Subtract with Carry |

| SUB<br>SUBB<br>SUBL       | dst, src                   | Subtract            |

Most of the instructions in this group perform an operation between a register operand and a second operand designated by any of the five basic addressing modes, and load the result into the register.

The arithmetic instructions in general alter the C, Z, S and P/V flags, which can then be tested by subsequent conditional jump instructions. The P/V flag is used to indicate arithmetic overflow for these instructions and it is referred to as the V (overflow) flag. The byte version of these instructions generally alters the D and H flags as well.

The basic integer (binary) operations are performed on byte, word or long word operands, although not all operand sizes are supported by all instructions. Multiple precision operations can be implemented in software using the Add with Carry, (ADC, ADCB),

Subtract with Carry (SBC, SBCB) and Extend Sign (EXTS, EXTSB, EXTSL) instructions.

BCD operations are not provided directly, but can be implemented using a binary addition (ADC, ADCB) or subtraction (SUBB, SBCB) followed by a decimal adjust instruction (DAB).

The Multiply and Divide instructions perform signed two's complement arithmetic on word or long word operands. The Multiply instruction (MULT) multiplies two 16-bit operands and produces a 32-bit result, which is loaded into the destination register pair. Similarly, Multiply Long (MULTL) multiplies two 32-bit operands and produces a 64-bit result, which is loaded into the destination register quadruple. An overflow condition is never generated by a multiply, nor can a true carry be generated. The carry flag is used instead to indicate where the product has too many significant bits to be contained entirely in the low-order half of the destination.

The Divide instruction (DIV) divides a 32-bit number in the destination register pair by a 16-bit source operand and loads a 16-bit guotient into the low-order half of the destination register. A 16-bit remainder is loaded into the high-order half. Divide Long (DIVL) operates similarly with a 64-bit destination register guadruple and a 32-bit source. The overflow flag is set if the quotient is bigger than the low-order half of the destination, or if the source is zero.

#### Logical Instructions.

| Instruction            | Operand(s) | Name of Instruction |

|------------------------|------------|---------------------|

| AND<br>ANDB            | dst, src   | And                 |

| COM<br>COMB            | dst        | Complement          |

| OR<br>ORB              | dst, src   | Or                  |

| TEST<br>TESTB<br>TESTL | dst        | Test                |

| XOR<br>XORB            | dst, src   | Exclusive Or        |

The instructions in this group perform logical operations on each of the bits of the operands. The operands may be bytes or words; logical operations on long word are not supported (except for TESTL) but are easily implemented with pairs of instructions.

The two-operand instructions, And (AND, ANDB), Or (OR, ORB) and Exclusive-Or (XOR,XORB) perform the appropriate logical operations on corresponding bits of the destination register and the source operand, which can be designated by any of four basic addressing modes (R, IR, DA, IM, X). The result is loaded into the destination register.

Complement (COM, COMB) complements the bits of the destination operand. Finally, Test (TEST, TESTB, TESTL) performs the OR operation between the destination operand and zero and sets the flags accordingly. The Complement and Test instructions can use four basic addressing modes to specify the destination.

The Logical instructions set the Z and S flags based on the result of the operation. The byte variants of these instructions also set the Parity Flag (P/V) if the parity of the result is even, while the word instructions leave this flag unchanged. The H and D flags are not affected by these instructions.

#### **Program Control Instructions.**

| Instruction   | Operand(s) | Name of Instruction               |

|---------------|------------|-----------------------------------|

| CALL          | dst        | Call Procedure                    |

| CALR          | dst        | Call Procedure Relative           |

| DJNZ<br>DBJNZ | r, dst     | Decrement and Jump if<br>Not Zero |

| IRET          |            | Interrupt Return                  |

| JP            | cc, dst    | Jump                              |

| JR            | cc, dst    | Jump Relative                     |

| RET           | сс         | Return from Procedure             |

| SC            | src        | System Call                       |

|               |            |                                   |

This group consists of the instructions that affect the Program Counter (PC) and thereby control program flow. General-purpose registers and memory are not altered except for the processor stack pointer and the processor stack, which play a significant role in procedures and interrupts. (An exception is Decrement and Jump if Not Zero (DJNZ), which uses a register as a loop counter.) The flags are also preserved except for IRET which réloads the program status, including the flags, from the processor stack.

The Jump (JP) and Jump Relative (JR) instructions provide a conditional transfer of control to a new location if the processor flags

statisfy the condition specified in the condition code field of the instruction. Jump Relative is a one-word instruction that will jump to any instruction within the range -254 to +256 bytes from the current location. Most conditional jumps in programs are made to locations only a few bytes away; the Jump Relative instruction exploits this fact to improve code compactness and efficiency.

Call and Call Relative are used for calling procedures; the current contents of the PC are pushed onto the processor stack, and the effective address indicated by the instruction is loaded into the PC. The use of a procedure address stack in this manner allows straightforward implementation of nested and recursive procedures. Like Jump Relative, Call Relative provides a one-word instruction for calling nearby subroutines. However, a much larger range, -4092 to +4098 bytes for CALR instruction, is provided since subroutine calls exhibit less locality than normal control transfers.

Both Jump and Call instructions are available with the indirect register, indexed and relative address modes in addition to the direct address mode. These can be useful for implementing complex control structures such as dispatch tables.

The Conditional Return instruction is a companion to the Call instruction; if the condition specified in the instruction is satisfied, it loads the PC from the stack and pops the stack.

A special instruction, Decrement and Jump if Not Zero (DJNZ, DBJNZ), implements the control part of the basic PASCAL FOR loop in a one-word instruction.

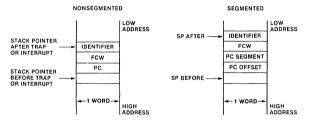

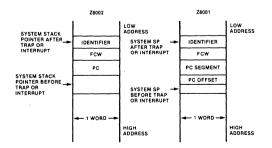

System Call (SC) is used for controlled access to facilities provided by the operating system. It is implemented identically to a trap or interrupt: the current program status is pushed onto the system processor stack followed by the instruction itself, and a new program status is loaded from a dedicated part of the Program Status Area. An 8-bit immediate source field in the instruction is ignored by the CPU hardware. It can be retrieved from the stack by the software which handles system calls and interpreted as desired, for example as an index into a dispatch table to implement a call to one of the services provided by the operating system. Interrupt Return (IRET) is used for returning from interrupts and traps, including system calls, to the interrupted routines. This is a privileged instruction.

#### **Bit Manipulation Instructions**

| Instruction   | Operand(s) | Name of Instruction |

|---------------|------------|---------------------|

| BIT<br>BITB   | dst, src   | Bit Test            |

| RES<br>RESB   | dst, src   | Reset Bit           |

| SET<br>SETB   | dst, src   | Set Bit             |

| TSET<br>TSETB | dst        | Test and Set        |

| TCC<br>TCCB   | cc, dst    | Test condition code |

The instructions in this group are useful for manipulating individual bits in registers or memory. In most computers, this has to be done using the logical instructions with suitable masks, which is neither natural nor efficient.

The Bit Set (SET, SETB) and Bit Reset (RES, RESB) instructions set or clear a single bit in the destination byte or word, which can be in a register or in a memory location specified by any of the five basic addressing modes. The particular bit to be manipulated may be specified statically by a value (0 to 7 for byte, 0 to 15 for word) in the instruction itself or it may be specified dynamically by the contents of a register, which could have been computed by previous instructions. In the latter case, the destination is restricted to a register. These instructions leave the flags unaffected. The companion Bit Test instruction (BIT, BITB) similarly tests a specified bit and sets the Z flag according to the state of the bit.

The Test and Set instruction (TSET, TSETB) is useful in multiprogramming and multiprocessing environments. It can be used for implementing synchronization mechanisms between processes on the same or different CPUs.

Another instruction in this group, Test Condition Code (TCC, TCCB) sets a bit in the destination register based on the state of the flags as specified by the condition code in the instruction. This may be used to control subsequent operation of the program after the flags have been changed by intervening

instructions. It may also be used by language compilers for generating boolean values.

| Rotate and S<br>Instruction | Shift Instructi<br>Operand(s) | ons.<br>Name of Instruction   |

|-----------------------------|-------------------------------|-------------------------------|

| RL<br>RLB                   | dst, src                      | Rotate Left                   |

| RLC<br>RLCB                 | dst, src                      | Rotate Left through<br>Carry  |

| RLDB                        | dst, src                      | Rotate Left Digit             |

| RR<br>RRB                   | dst, src                      | Rotate Right                  |

| RRC<br>RRCB                 | dst, src                      | Rotate Right through<br>Carry |

| RRDB                        | dst, src                      | Rotate Right Digit            |

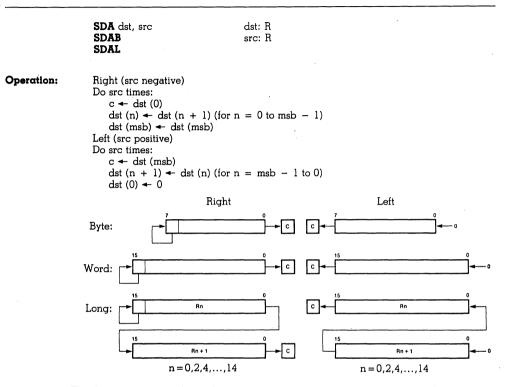

| SDA<br>SDAB<br>SDAL         | dst, src                      | Shift Dynamic Arithmetic      |

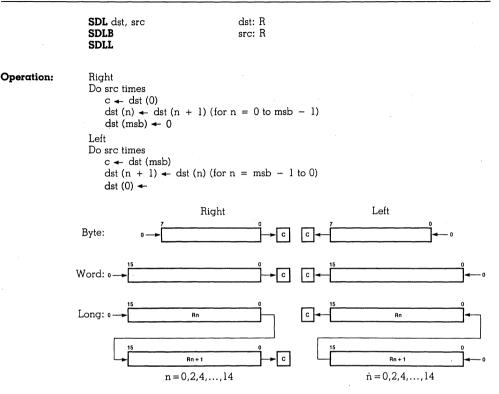

| SDL<br>SDLB<br>SDLL         | dst, src                      | Shift Dynamic Logical         |

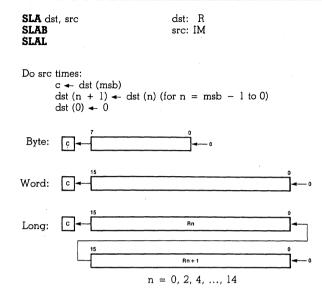

| SLA<br>SLAB<br>SLAL         | dst, src                      | Shift Left Arithmetic         |

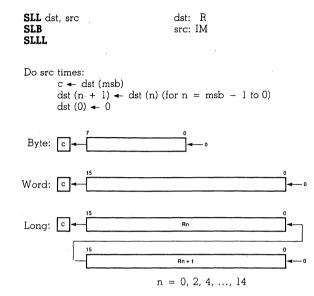

| SLL<br>SLLB<br>SLLL         | dst, src                      | Shift Left Logical            |

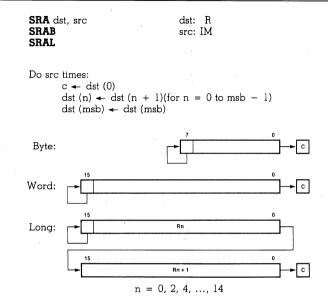

| SRA<br>SRAB<br>SRAL         | dst, src                      | Shift Right Arithmetic        |

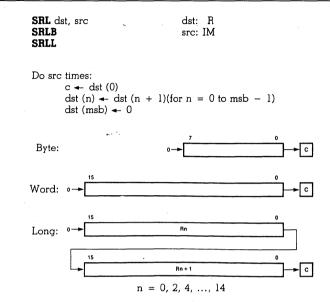

| SRL<br>SRLB<br>SRLL         | dst, src                      | Shift Right Logical           |

This group contains a rich repertoire of instructions for shifting and rotating data registers.

Instructions for shifting arithmetically or logically in either direction are available. Three operand lengths are supported: 8, 16 and 32 bits. The amount of the shift, which may be any value up to the operand length, can be specified statically by a field in the instruction or dynamically by the contents of a register. The ability to determine the shift amount dynamically is a useful feature, which is not available in most minicomputers.

The rotate instructions will rotate the contents of a byte or word register in either direction by one or two bits; the carry bit can be included in the rotation. A pair of digit rotation instructions (RLDB, RRDB) are especially useful in manipulating BCD data.

### Block Transfer And String Manipulation Instructions.

| Instruction     | 5.               |                                          |

|-----------------|------------------|------------------------------------------|

| Instruction     | Operand(s)       | Name of Instruction                      |

| CPD<br>CPDB     | dst, src, r, cc  | Compare and Decrement                    |

| CPDRB           | dst, src, r, cc̀ | Compare, Decrement and<br>Repeat         |

| CPI<br>CPIB     | dst, src, r, cc  | Compare and Increment                    |

| CPIR<br>CPIRB   | dst, src, r, cc  | Compare, Increment and<br>Repeat         |

| CPSD<br>CPSDB   | dst, src, r, cc  | Compare String and<br>Decrement          |

| CPSDR<br>CPSDRB | dst, src, r, cc  | Compare String,<br>Decrement and Repeat  |

| CPSI<br>CPSIB   | dst, src, r, cc  | Compare String and<br>Increment          |

| CPSIR<br>CPSIRB | dst, src, r, cc  | Compare String,<br>Increment and Repeat  |

| LDD<br>LDDB     | dst, src, r      | Load and Decrement                       |

| LDDR<br>LDRB    | dst, src, r      | Load, Decrement and<br>Repeat            |

| LDI<br>LDIB     | dst, src, r      | Load and Increment                       |

| LDIR<br>LDIRB   | dst, src, r      | Load, Increment and<br>Repeat            |

| TRDB            | dst, src, r      | Translate and Decrement                  |

| TRDRB           | dst, src, r      | Translate, Decrement and<br>Repeat       |

| TRIB            | dst, src, r      | Translate and Increment                  |

| TRIRB           | dst, src, r      | Translate, Increment and<br>Repeat       |

| TRTDB           | srcl, src2, r    | Translate, Test and<br>Decrement         |

| TRTDRB          | srcl, src2, r    | Translate, Test,<br>Decrement and Repeat |

| TRTIB           | srcl, src2, r    | Translate, Test and<br>Increment         |

| TRTIRB          | srcl, src2, r    | Translate, Test, Increment<br>and Repeat |

This is an exceptionally powerful group of instructions that provides a full complement of string comparison, string translation and block transfer functions. Using these instructions, a byte or word block of any length up to 64K bytes can be moved in memory; a byte or word string can be searched until a given value is found; two byte or word strings can be compared; and a byte string can be translated by using the value of each byte as the address of

its own replacement in a translation table. The more complex Translate and Test instructions skip over a class of bytes specified by a translation table, detecting bytes with values of special interest.

All the operations can proceed through the data in either direction. Furthermore, the operations may be repeated automatically while decrementing a length counter until it is zero, or they may operate on one storage unit per execution with the length counter decremented by one and the source and destination pointer registers properly adjusted. The latter form is useful for implementing more complex operations in software by adding other instructions within a loop containing the block instructions.

Any word register can be used as a length counter in most cases. If the execution of the instruction causes this register to be decremented to zero, the P/V flag is set. The autorepeat forms of these instructions always leave this flag set.

The D and H flags are not affected by any of these instructions. The C and S flags are preserved by all but the compare instructions.

These instructions use the Indirect Register (IR) addressing mode: the source and destination operands are addressed by the contents of general-purpose registers (word registers in nonsegmented mode and register pairs in segmented mode). Note that in the segmented mode, only the low-order half of the register pair gets incremented or decremented as with all address arithmetic in the Z8000.

The repetitive forms of these instructions are interruptible. This is essential since the repetition count can be as high as 65,536 and the instructions can take 9 to 14 cycles for each iteration after the first one. The instruction can be interrupted after any iteration. The address of the instruction itself, rather than the next one, is saved on the stack, and the contents of the operand pointer registers, as well as the repetition counter, are such that the instruction can simply be reissued after returning from the interrupt without any visible difference in its effect.

This group consists of instructions for transferring a byte, word or block of data between peripheral devices and the CPU registers or memory. Two separate I/O address spaces with 16-bit addresses are recognized, a Standard I/O address space and a Special I/O address space. The latter is intended for use with special Z8000 Family devices, typically the Z-MMU. Instructions that operate on the Special I/O address space are prefixed with the word "special." Standard I/O and Special I/O instructions generate different codes on the CPU status lines. Normal 8-bit peripherals

#### Input/Output Instructions.

| Input/Output Instructions. |             |                                         |  |  |  |

|----------------------------|-------------|-----------------------------------------|--|--|--|

| Instruction                | Operand(s)  | Name of Instruction                     |  |  |  |

| IN<br>INB                  | dst, src    | Input .                                 |  |  |  |

| IND<br>INDB                | dst, src, r | Input and Decrement                     |  |  |  |

| INDR<br>INDRB              | dst, src, r | Input, Decrement and<br>Repeat          |  |  |  |

| INI<br>INIB                | dst, src, r | Input and Increment                     |  |  |  |

| INIR<br>INIRB              | dst, src, r | Input, Increment and<br>Repeat          |  |  |  |

| OTDR<br>OTDRB              | dst, src, r | Output, Decrement and<br>Repeat         |  |  |  |

| OTIR<br>OTIRB              | dst, src, r | Output, Increment and<br>Repeat         |  |  |  |

| OUT<br>OUTB                | dst, src    | Output                                  |  |  |  |

| OUTD<br>OUTDB              | dst, src, r | Output and Decrement                    |  |  |  |

| OUTI<br>OUTIB              | dst, src, r | Output and Increment                    |  |  |  |

| SIN<br>SINB                | dst, src    | Special Input                           |  |  |  |

| SIND<br>SINDB              | dst, src, r | Special Input and<br>Decrement          |  |  |  |

| SINDR<br>SINDRB            | dst, src, r | Special Input, Decrement<br>and Repeat  |  |  |  |

| SINI<br>SINIB              | dst, src, r | Special Input and<br>Increment          |  |  |  |

| SINIR<br>SINIRB            | dst, src, r | Special Input, Increment<br>and Repeat  |  |  |  |

| SOTDR<br>SOTDRB            | dst, src, r | Special Output,<br>Decrement and Repeat |  |  |  |

| SOTIR<br>SOTIRB            | dst, src, r | Special Output,<br>Increment and Repeat |  |  |  |

| SOUT<br>SOUTB              | dst, src    | Special Output                          |  |  |  |

| SOUTD<br>SOUTDB            | dst, src, r | Special Output and<br>Decrement         |  |  |  |

| SOUTI<br>SOUTIB            | dst, src, r | Special Output and<br>Increment         |  |  |  |

are connected to bus lines  $AD_0-AD_7$ . Standard I/O byte instructions use odd addresses only. Special 8-bit peripherals such as the MMU, which are used with special I/O instructions, are connected to bus lines  $AD_8-AD_{15}$ . Special I/O byte instructions use even addresses only.

The instructions for transferring a single byte or word (IN, INB, OUT, OUTB, SIN, SINB, SOUT, SOUTB) can transfer data between any general-purpose register and any port in either address space. For the Standard I/O instructions, the port number may be specified statically in the instruction or dynamically by the contents of the CPU register. For the Special I/O instructions the port number is specified statically.

The remaining instructions in this group form a powerful and complete complement of instructions for transferring blocks of data between I/O ports and memory. The operation of these instructions is very similar to that of the block move instructions described earlier, with the exception that one operand is always an I/O port which remains unchanged as the address of the other operand (a memory location) is incremented or decremented. These instructions are also interruptible.

#### **CPU** Control Instructions.

| Instruction     | Operand(s) | Name of Instruction   |

|-----------------|------------|-----------------------|

| COMFLG          | flag       | Complement Flag       |

| DI              | int        | Disable Interrupt     |

| EI              | int        | Enable Interrupt      |

| HALT            |            | Halt                  |

| LDCTL<br>LDCTLB | dst, src   | Load Control Register |

| LDPS            | src        | Load Program Status   |

| MBIT            |            | Multi-Micro Bit Test  |

| MREQ            | dst        | Multi-Micro Request   |

| MRES            |            | Multi-Micro Reset     |

| MSET            |            | Multi-Micro Set       |

| NOP             |            | No Operation          |

| RESFLG          | flag       | Reset Flag            |

| SETFLG          | flag       | Set Flag              |

All I/O instructions are privileged, i.e. they can only be executed in system mode. The single byte/word I/O instructions don't alter any flags. The block I/O instructions, including the single iteration variants, alter the Z and P/V flags. The latter is set when the repetition counter is decremented to zero.

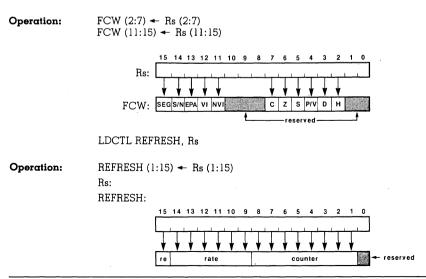

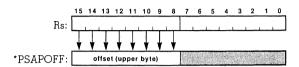

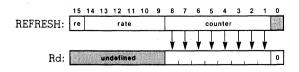

The instructions in this group relate to the CPU control and status registers (FCW, PSAP, REFRESH, etc.), or perform other unusual functions that do not fit into any of the other groups, such as instructions that support multimicroprocessor operation. Most of these instructions are privileged, with the exception of NOP and the instructions operating on the flags (SETFLG, RESFLG, COMFLG, LDCTLB).

**Extended Instructions.** The Z8000 architecture includes a powerful mechanism for extending the basic instruction set through the use of external devices known as Extended Processing Units (EPUs). A group of six opcodes, OE, OF, 4E, 4F, 8E and 8F (in hexadecimal), is dedicated for the implementation of extended instructions using this facility. The five basic addressing modes (R, IR, DA, IM and X) can be used by extended instructions for accessing data for the EPUs.

There are four types of extended instructions in the Z8000 CPU instruction repertoire: EPU internal operations; data transfers between memory and EPU; data transfers between EPU and CPU; and data transfers between EPU flag registers and CPU flag and control word. The last type is useful when the program must branch based on conditions determined by the EPU. The action taken by the CPU upon encountering extended instructions is dependent upon the EPA control bit in the CPU's FCW. When this bit is set, it indicates that the system configuration includes EPUs; therefore, the instruction is executed. If this bit is clear, the CPU traps (extended instruction trap) so that a trap handler in software can emulate the desired operation.

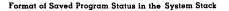

#### **Processor Flags**

The processor flags are a part of the program status. They provide a link between sequentially executed instructions in the sense that the result of executing one instruction may alter the flags, and the resulting value of the flags may be used to determine the operation of a subsequent instruction, typically a conditional jump instruction. An example is a Test followed by a Conditional Jump:

| TEST RI    | !sets Z flag if R1 = 0!          |

|------------|----------------------------------|

| JR Z, DONE | lgo to DONE if Z flag is<br>set! |

#### DONE:

The program branches to DONE if the TEST sets the Z flag, i.e., if R1 contains zero.

The program status has six flags for the use of the programmer and the Z8000 processor:

- Carry (C)

- Zero (Z)

- Sign (S)

- Parity/Overflow (P/V)

- Decimal Adjust (D)

- Half Carry (H)

The flags are modified by many instructions, including the arithmetic and logical instructions.

Appendix C lists the instructions and the flags they affect. In addition, there are Z8000 CPU control instructions which allow the programmer to set, reset (clear), or complement any or all of the first four flags. The Half-Carry and Decimal-Adjust flags are used by the Z8000 processor for BCD arithmetic corrections. They are not used explicitly by the programmer.

The FLAGS register can be separately loaded by the Load Control Register (LDCTLB) instruction without disturbing the control bits in the other byte of the FCW. The contents of the flag register may also be saved in a register or memory.

The Carry (C) flag, when set, generally indicates a carry out of or a borrow into the highorder bit position of a register being used as an accumulator. For example, adding the 8-bit numbers 225 and 64 causes a carry out of bit 7 and sets the Carry flag:

|             |             |   | 1        | Bit |   |   |   |   |  |

|-------------|-------------|---|----------|-----|---|---|---|---|--|

|             | 7           | 6 | 5        | 4   | 3 | 2 | 1 | 0 |  |

| 225<br>+ 64 | 1           | 1 | 1        | 0   | 0 | 0 | 0 | 1 |  |

| 289         |             |   |          | 0   | 0 | 0 | 0 | 1 |  |

|             | <b>L</b> ►1 | = | Carry fl | ag  |   |   |   |   |  |

The Carry flag plays an important role in the implementation of multiple-precision arithmetic (see the ADC, SBC instructions). It is also involved in the Rotate Left Through Carry (RLC) and Rotate Right Through Carry (RRC) instructions. One of these instructions is used to implement rotation or shifting of long strings of bits.

The Zero (Z) flag is set when the result register's contents are zero following certain operations. This is often useful for determining when a counter reaches zero. In addition, the block compare instructions use the Z flag to indicate when the specified comparison condition is satisfied.

The Sign (S) flag is set to one when the most significant bit of a result register contains a one (a negative number in two's complement notation) following certain operations.

The Overflow (V) flag, when set, indicates that a two's complement number in a result register has exceeded the largest number or is less than the smallest number that can be represented in a two's complement notation. This flag is set as the result of an arithmetic operation. Consider the following example:

|      |   |   |        | Bit     |   |   |    |   |

|------|---|---|--------|---------|---|---|----|---|

|      | 7 | 6 | 5      | 4       | 3 | 2 | .1 | 0 |

| 120  | 0 | 1 | 1      | 0       | 1 | 0 | 0  | 1 |

| +105 | 0 | 1 | 1      | 0       | 1 | 0 | 0  | 1 |

| 225  |   | 1 | 1      | 0       | 0 | 0 | 0  | 1 |

|      |   | = | Overfl | ow flag | 1 |   |    |   |

The result in this case (-95 in two's complement notation) is incorrect, thus the overflow flag would be set.

The same bit acts as a Parity (P) flag following logical instructions on byte operands. The number of one bits in the register is counted and the flag is set if the total is even (that is, P = 1). If the total is odd (P = 0), the flag is reset. This flag is often referred to as the P/V flag.

#### Processor Flags (Continued)

The Block Move and String instructions and the Block I/O instructions use the P/V flag to indicate the repetition counter has decremented to 0.

The Decimal-Adjust (D) flag is used for BCD arithmetic. Since the algorithm for correcting BCD operations is different for addition and subtraction, this flag is used to record whether an add or subtract instruction was executed so that the subsequent Decimal Adjust (DAB) instruction can perform its function correctly (See the DAB instruction for further discussion

#### on the use of this flag).

The Half-Carry (H) flag indicates a carry out of bit 3 or a borrow into bit 3 as the result of adding or subtracting bytes containing two BCD digits each. This flag is used by the DAB instruction to convert the binary result of a previous decimal addition or subtraction into the correct decimal (BCD) result.

Neither the Decimal-Adjust nor the Half-Carry flag is normally accessed by the programmer.

#### **Condition Codes**

The first four flags, C, Z, S, and P/V, are used to control the operation of certain "conditional" instructions such as the Conditional Jump. The operation of these instructions is a function of whether a specified boolean condition on the four flags is satisfied or not. It would take 16 bits to specify any of the 65,536 (2<sup>16</sup>) boolean functions of the four flags. Since only a very small fraction of these are generally of interest, this procedure would be very wasteful. Sixteen functions of the flag settings found to be frequently useful are encoded in a 4-bit field called the condition code, which

#### Instruction Interrupts and Traps

This section looks at the relation-ship between instructions ans interrupts.

When the CPU receives an interrupt request, and it is enabled for interrupts of that class, the interrupt is normally processed at the end of the current instruction. However, certain instructions which might take a long time to complete are designed to be interruptible so as to minimize the length of time it takes the CPU to respond to an interrupt. These are the iterative versions of the String and Block instructions and the Block I/O instruction. If an interrupt request is received during one of these interruptible instructions, the instruction is suspended after the current iteration. The address of the instruction itself, rather than the address of the following instruction, is saved on the stack, so that the same instruction is executed again when the interrupt handler executes an IRET. The conforms a part of all conditional instructions.

The condition codes and the flag settings they represent are listed in Section 6.6.

Although there are sixteen unique condition codes, the assembler recognizes more than sixteen mnemonics for the conditional codes. Some of the flag settings have more than one meaning for the programmer, depending on the context (PE & OV, Z & EQ, C & ULT, etc.). Program clarity is enhanced by having separate mnemonics for the same binary value of the condition codes in these cases.

tents of the repetition counter and the registers which index into the block operands are such that after each iteration when the instruction is reissued upon returning from an interrupt, the effect is the same as if the instruction were not interrupted. This assumes, of course, the interrupt handler preserved the registers, which is a general requirement on interrupt handlers.

The longest noninterruptible instruction that can be used in normal mode is Divide Long (749 cycles in the worst case). Multi-Micro-Request, a privileged instruction, can take longer depending on the contents of the destination register.

Traps are synchronous events that result from the execution of an instruction. The action of the CPU in response to a trap condition is similar to the case of an interrupt (see Section 7). Traps are non-maskable.

#### Instruction Interrupts and Traps (Continued)

The Z8000 CPUs implement four kinds of traps:

- Extended Instruction

- Privileged Instruction in normal mode

- Segmentation violation

- System Call

The Extended Instruction trap occurs when an Extended Instruction is encountered, but the Extended Processor Architecture Facility is disabled, i.e., the EPA bit in the FCW is a zero. This allows the same software to be run on Z8000 system configurations with or without EPUs. On systems without EPUs, the desired extended instructions can be emulated by software which is invoked by the Extended Instruction trap.

#### **Notation and Binary Encoding**

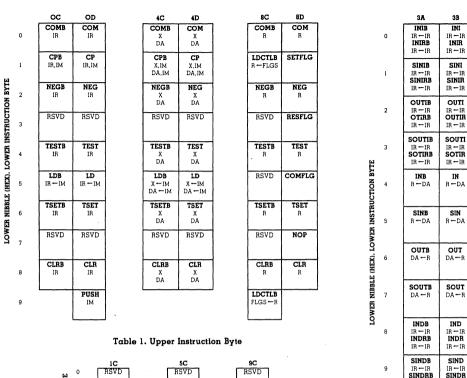

The rest of this chapter consists of detailed descriptions of each instruction, listed in alphabetical order. This section describes the notational conventions used in the instruction descriptions and the binary encoding for some of the common instruction fields (e.g., register designation fields).

The description of an instruction begins with the instruction mnemonic and instruction name in the top part of the page. Privileged instructions are also identified at the top.

The assembler language syntax is then given in a single generic form that covers all the variants of the instruction, along with a list of applicable addressing modes.

Example:

| AND dst, src | dst: | R  |     |     |     |   |  |

|--------------|------|----|-----|-----|-----|---|--|

| ANDB         | src: | R, | IM, | IR, | DA, | Х |  |

The operation of the instruction is presented next, followed by a detailed discussion of the instruction.

The next part specifies the effect of the instruction on the processor flags. This is followed by a table that presents all the variants of the instruction for each applicable addressing mode and operand size. For each of these variants, the following information is provided:

**A. Assembler Language Syntax.** The syntax is shown for each applicable operand width

The privileged instruction trap serves to protect the integrity of a system from erroneous or unauthorized actions of arbitrary processes. Certain instructions, called privileged instructions, can only be executed in system mode. An attempt to execute one of these instructions in normal mode causes a privileged instruction trap. All the I/O instructions and most of the instructions that operate on the FCW are privileged, as are instructions like HALT and IRET.

The System Call instruction always causes a trap. It is used to transfer control to system mode software in a controlled way, typically to request supervisor services.

(byte, word or long). The invariant part of the syntax is given in UPPER CASE and must appear as shown. Lower case characters represent the variable part of the syntax, for which suitable values are to be substituted. The syntax shown is for the most basic form of the instruction recognized by the assembler. For example,

ADD Rd,#data

represents a statement of the form ADD R3,#35. The assembler will also accept variations like ADD TOTAL, #NEW-DELTA where TOTAL, NEW and DELTA have been suitably defined.

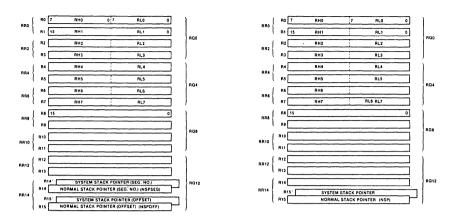

The following notation is used for register operands:

| Rd, Rs, etc.: | a word register in the range R0-R15                      |

|---------------|----------------------------------------------------------|

| Rbd Rbs:      | a byte register RHn or                                   |

| RRd RRs:      | RLn where n = 0 - 7<br>a register pair RR0, RR2,<br>RR14 |

| RQd:          | a register quadruple<br>RQ0, RQ4, RQ8 or RQ12            |

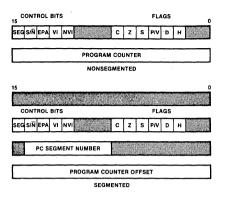

The "s" or "d" represents a source or destination operand. Address registers used in Indirect, Base and Base Index addressing modes represent word registers in nonsegmented mode and register pairs in segmented mode. A one-word register used in segmented

#### Notation and Binary Encoding (Continued)

mode is flagged and a footnote explains the situation.

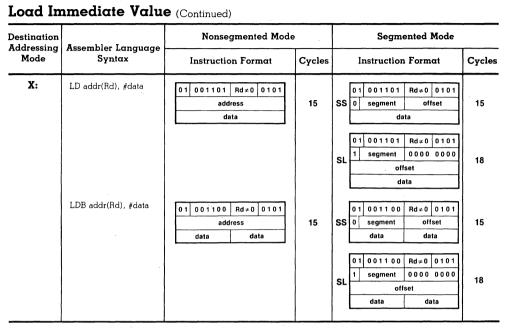

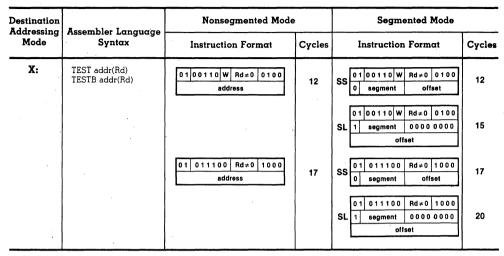

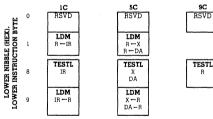

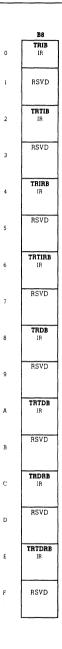

**B.** Instruction Format. The binary encoding of the instruction is given in each case for both the nonsegmented and segmented modes. Where applicable, both the short and long forms of the segmented version are given (SS and SL).

The instruction formats for byte and word versions of an instruction are usually combined. A single bit, labeled "w," distinguishes them: a one indicates a word instruction, while a zero indicates a byte instruction.

Fields specifying register operands are identified with the same symbols (Rs, RRd, etc.) as in Assembler Language Syntax. In some cases, only honzero values are permitted for certain registers, such as index registers. This is indicated by a notation of the form "RS  $\neq 0."$

The binary encoding for register fields is as follows:

| Register |     |    |     | Binary |

|----------|-----|----|-----|--------|

| RQ0      | RRO | RO | RH0 | 0000   |

|          |     | R1 | RH1 | 0001   |

|          | RR2 | R2 | RH2 | 0010   |

|          |     | R3 | RH3 | 0011   |

|      | Regi |     | Binary |      |

|------|------|-----|--------|------|

| RQ4  | RR4  | R4  | RH4    | 0100 |

|      |      | R5  | 'RH5   | 0101 |

|      | RR6  | R6  | RH6    | 0110 |

|      |      | R7  | RH7    | 0111 |

| RQ8  | RR8  | R8  | RLO    | 1000 |

|      |      | R9  | RL1    | 1001 |

|      | RR10 | R10 | RL2    | 1010 |

|      |      | R11 | RL3    | 1011 |

| RQ12 | RR12 | R12 | RL4    | 1100 |

|      |      | R13 | RL5    | 1101 |

|      | RR14 | R14 | RL6    | 1110 |

|      |      | R15 | RL7    | 1111 |

For easy cross-references, the same symbols are used in the Assembler Language Syntax and the instruction format. In the case of addresses, the instruction format in segmented mode uses "segment" and "offset" to correspond to "address," while the instruction format contains "displacement," indicating that the assembler has computed the displacement and inserted it as indicated.

A condition code is indicated by "cc" in both the Assembler Language Syntax and the instruction formats. The condition codes, the flag settings they represent, and the binary encoding in the instruction are as follows:

#### Notation and Binary Encoding (Continued)

| c        | ode | Meaning                              | Flag Setting              | Binary |

|----------|-----|--------------------------------------|---------------------------|--------|

| F        |     | Always false                         |                           | 0000   |

|          |     | Always true                          |                           | 1000   |

| Z        |     | Zero                                 | Z = 1                     | 0110   |

| N        | Z   | Not zero                             | Z = 0                     | 1110   |

| C        | 3   | Carry                                | C = 1                     | . 0111 |

| N        | IC  | No carry                             | C = 0                     | 1111   |

| P        | L   | Plus                                 | S = 0                     | 1101   |

| M        | ſI  | Minus                                | S = 1                     | 0101   |

| N        | E   | Not equal                            | Z = 0                     | 1110   |

| E        | Q   | Equal                                | Z = 1                     | 0110   |

| C        | V   | Overflow                             | V = 1                     | 0100   |

| N        | OV  | No overflow                          | V = 0                     | 1100   |

| P        | E   | Parity even                          | P = 1                     | 0100   |

| P        | Ó   | Parity odd                           | P = 0                     | 1100   |

| G        | Ε   | Greater than<br>or equal             | (S XOR V) = 0             | 1001   |

| L        | Т   | Less than                            | (S XOR V) = 1             | 0001   |

| G        | Τ   | Greater than                         | (Z  OR  (S  XOR  V)) = 0  | 1010   |

| L        | E   | Less than or<br>equal                | (Z  OR  (S  XOR  V)) = 1  | 0010   |

| <u>U</u> | GE  | Unsigned<br>greater than<br>or equal | C = 0                     | 1111   |

| U        | ILT | Unsigned<br>less than                | C = 1                     | 0111   |

| U        | GT  | Unsigned<br>greater than             | ((C = 0) AND (Z = 0)) = 1 | 1011   |

| U        | ILE | Unsigned less<br>than or equal       | (C  OR  Z) = 1            | 0011   |

Note that some of the condition codes correspond to identical flag settings: i.e., Z-EQ, NZ-NE, NC-UGE, PE-OV, PO-NOV.

**C. Cycles.** This line gives the execution time of the instructions in CPU cycles.

**D. Example.** A short assembly language example is given showing the use of the instruction.

#### Z8000 Instruction Descriptions and Formats

# ADC Add With Carry

|            | ADC dst, src<br>ADCB                                                                                                    | dst: R<br>src: R                                                                                                                                                                                                                                                                                               |                                                                                                             |

|------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Operation: | dst 🛶 dst + sr                                                                                                          | c + c                                                                                                                                                                                                                                                                                                          |                                                                                                             |

|            | tion operand ar<br>not affected. Tv<br>metic, this instr                                                                | rand, along with the setting of the<br>add the sum is stored in the destination<br>vo's complement addition is perform<br>uction permits the carry from the ar<br>the addition of high-order operand                                                                                                           | on. The contents of the source are<br>ned. In multiple precision arith-<br>ddition of low-order operands to |

| Flags:     | otherwise<br>Z: Set if the res<br>S: Set if the res<br>V: Set if arithm<br>and the resu<br>D: ADC—unaff<br>H: ADC—unaff | is a carry from the most significant is<br>sult is zero; cleared otherwise<br>sult is negative; cleared otherwise<br>etic overflow occurs, that is, if both<br>it is of the opposite sign; cleared of<br>ected; ADCB—cleared<br>ected; ADCB—set if there is a carr;<br>er four bits of the result; cleared oth | operands were of the same sign<br>therwise<br>y from the most significant bit of                            |

|            |                                                                                                                         | Noncogmonted Mode                                                                                                                                                                                                                                                                                              | Sogmonted Mode                                                                                              |

| Addressing Assembler Language |                             | Nonsegmented Mode  |        | Segmented Mode     |        |  |

|-------------------------------|-----------------------------|--------------------|--------|--------------------|--------|--|

| Mode                          | Syntax                      | Instruction Format | Cycles | Instruction Format | Cycles |  |

| R:                            | ADC Rd, Rs<br>ADCB Rbd, Rbs | 10 11010 W Rs Rd   | 5      | 10 11010 W Rs Rd   | 5      |  |

Example:

Long addition can be done with the following instruction sequence, assuming R0, R1 contain one operand and R2, R3 contain the other operand:

| ADD | R1,R3 | !add low-order words!           |

|-----|-------|---------------------------------|

| ADC | R0,R2 | add carry and high-order words! |

If R0 contains %0000, R1 contains %FFFF, R2 contains %4320 and R3 contains %0001, then the above two instructions leave the value %4321 in R0 and %0000 in R1.

#### ADD Add ADD dst, src dst: R src: R, IM, IR, DA, X ADDB ADDL **Operation:** dst - dst + src The source operand is added to the destination operand and the sum is stored in the destination. The contents of the source are not affected. Two's complement addition is performed. Flags: C: Set if there is a carry from the most significant bit of the result; cleared otherwise Z: Set if the result is zero; cleared otherwise S: Set if the result is negative; cleared otherwise V: Set if arithmetic overflow occurs, that is, if both operands were of the same sign and the result is of the opposite sign; cleared otherwise D: ADD, ADDL-unaffected; ADDB-cleared

**H:** ADD, ADDL—unaffected; ADDB—set if there is a carry from the most significant bit of the low-order four bits of the result; cleared otherwise

| Source             |                                | Nonsegmented Mode                                                                                                                         |        | Segmented Mode                                                                                                                            |        |  |

|--------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|--------|--|

| Addressing<br>Mode | Assembler Language<br>Syntax   | Instruction Format                                                                                                                        | Cycles | Instruction Format                                                                                                                        | Cycles |  |

| R:                 | ADD Rd, Rs<br>ADDB Rbd, Rbs    | 1000000W Rs Rd                                                                                                                            | 4      | 100000W Rs Rd                                                                                                                             | 4      |  |

|                    | ADDL RRd, RRs                  | 10 010110 RRs RRd                                                                                                                         | 8      | 10 010110 RRs RRd                                                                                                                         | 8      |  |

| IM:                | ADD Rd, #data                  | 00 00001 0000 Rd<br>data                                                                                                                  | 7      | 00 000001 0000 Rd<br>data                                                                                                                 | 7      |  |

|                    | ADDB Rbd, #data                | 00 00000 0000 Rd<br>data data                                                                                                             | ,7     | 00 00000 0000 Rd<br>data data                                                                                                             | 7      |  |

|                    | ADDL RRd, #data                | 0.0         0.1.0.1.1.0         0.0.0.0         RRd           31         data (high)         16           15         data (low)         0 | 14     | 0.0         0.1.0.1.1.0         0.0.0.0         RRd           31         data (high)         16           15         data (low)         0 | 14     |  |

| IR:                | ADD Rd, @Rs1<br>ADDB Rbd, @Rs1 | 0000000W Rs≠0 Rd                                                                                                                          | 7      | 000000W Rs≠0 Rd                                                                                                                           | 7      |  |

|                    | ADDL RRd, @Rs1                 | 00 010110 Rs≠0 RRd                                                                                                                        | 14     | 00 010110 Rs≠0 RRd                                                                                                                        | 14     |  |

# ADD Add

| Source<br>Addressing | Assembler Language                     | Nonsegmented Mode                  |        | Segmented Mode                                                                                                       |        |  |

|----------------------|----------------------------------------|------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------|--------|--|

| Mode                 | Syntax                                 | Instruction Format                 | Cycles | Instruction Format                                                                                                   | Cycles |  |

| DA:                  | ADD Rd, address<br>ADDB Rbd, address   | 0100000 W 0000 Rd<br>address       | 9      | SS 0 1 0 0 0 0 0 W 0 0 0 0 0 Rd<br>0 segment offset                                                                  | 10     |  |

|                      |                                        |                                    |        | 01         00000         W         0000         Rd           1         segment         00000000         offset       | 12     |  |

|                      | ADDL RRd, address                      | 01 010110 0000 RRd<br>address      | 15     | SS 0 1 0 1 0 1 1 0 0 0 0 0 RRd<br>0 segment offset                                                                   | 16     |  |

|                      |                                        | ·                                  |        | 01         010110         0000         RRd           1         segment         0000000         offset                | 18     |  |

| <b>X</b> :           | ADD Rd, addr(Rs)<br>ADDB Rbd, addr(Rs) | 0 1 0 0 0 0 0 W Rs≠0 Rd<br>address | 10     | SS <mark>010000W Rs≠0 Rd<br/>0 segment offset</mark>                                                                 | 10     |  |

|                      |                                        |                                    |        | 01         0000         W         Rs≠0         Rd           1         segment         000000         offset          | 13     |  |

|                      | ADDL RRd, addr(Rs)                     | 01 010110 Rs≠0 RRd<br>address      | 16     | SS 01 010110 Rs≠0 RRd<br>0 segment offset                                                                            | 16     |  |

|                      |                                        |                                    |        | 01         0101010         Rs≠0         RRd           SL         1         segment         00000000           offset | 19     |  |

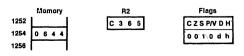

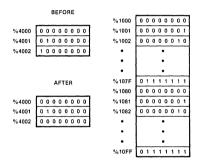

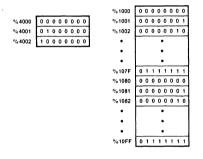

Example:

ADD R2, AUGEND !augend A located at %1254! Before instruction execution:

After instruction execution:

# AND And

|            | AND dst, src<br>ANDB          | dst: R<br>src: R, IM, IR, DA, X                                                                                                                                                                        |

|------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation: | dst 🗕 dst AND src             |                                                                                                                                                                                                        |

|            | and destination operands, and | formed between the corresponding bits of the source<br>the result is stored in the destination. A one bit is<br>ding bits in the two operands are both ones; otherwise<br>e contents are not affected. |

| Flags:     |                               | red otherwise<br>t of the result is set; cleared otherwise<br>— set if parity of the result is even; cleared otherwise                                                                                 |

| Source             | 8                                      | Nonsegmented Mode                     |        | Segmented Mode                                                                                                                       |        |

|--------------------|----------------------------------------|---------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|--------|

| Addressing<br>Mode | Assembler Language<br>Syntax           | Instruction Format                    | Cycles | Instruction Format                                                                                                                   | Cycles |

| R:                 | AND Rd, Rs<br>ANDB Rbd, Rs             | 1000011WRsRd                          | 4      | 1000011W Rs Rd                                                                                                                       | 4      |

| IM:                | AND Rd, #data                          | 00 000111 0000 Rd<br>data             | 7      | 00 000111 0000 Rd<br>data                                                                                                            | 7      |

|                    | ANDB Rbd, #data                        | 00 000110 0000 Rd<br>data data        | 7      | 00 000110 0000 Rd<br>data data                                                                                                       |        |

| IR:                | AND Rd, @Rs1<br>ANDB Rbd, @Rs1         | 0000011 W Rs≠0 Rd                     | 7      | 0000011W Rs≠0 Rd                                                                                                                     | 7      |

| DA:                | AND Rd, address<br>ANDB Rbd, address   | 0 1 0 0 0 1 1 W 0 0 0 0 Rd<br>address | 9      | SS 0 1 0 0 0 1 1 W 0 0 0 0 Rd<br>0 segment offset                                                                                    | 10     |

|                    |                                        |                                       |        | 0100011         W         0000         Rd           1         segment         0000         0000           offset                     | 12     |

| X:                 | AND Rd, addr(Rs)<br>ANDB Rbd, addr(Rs) | 0 1 0 0 0 1 1 W Rs≠0 Rd<br>address    | 10     | SS         0 1 0 0 0 1 1 W Rs ≠ 0 Rd           0 segment         offset                                                              | 10     |

|                    |                                        |                                       |        | 01         00011         W         Rs≠0         Rd           SL         1         segment         0000         0000           offset | 13     |

#### **Example:** ANDB RL3, # %CE

Before instruction execution:

| RL3             | Flags    |

|-----------------|----------|

| 1 1 1 0 0 1 1 1 | CZSP/VDH |

|                 | czspdh   |

After instruction execution:

| RL3      | Flags       |

|----------|-------------|

| 11000110 | CZSP/VDH    |

|          | c 0 1 1 d h |

# BIT Bit Test

BIT dst, src BITB dst: R, IR, DA, X src: IM or dst: R src: R Operation: Z ← NOT dst (src)

The specified bit within the destination operand is tested, and the Z flag is set to one if the specified bit is zero; otherwise the Z flag is cleared to zero. The contents of the destination are not affected. The bit number (the source) can be specified statically as an immediate value, or dynamically as a word register whose contents are the bit number. In the dynamic case, the destination operand must be a register, and the source operand must be R0 through R7 for BITB, or R0 through R15 for BIT. The bit number is a value from 0 to 7 for BITB, or 0 to 15 for BIT, with 0 indicating the least significant bit. Note that only the lower four bits of the source operand are used to specify the bit number for BIT, while only the lower three bits of the source operand are used for BITB.

Flags:

C: Unaffected

Z: Set if specified bit is zero; cleared otherwise

S: Unaffected

V: Unaffected

D: Unaffected

H: Unaffected

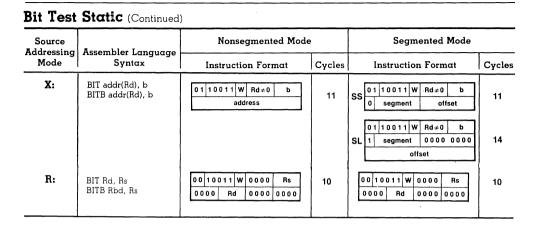

#### **Bit Test Static**

| Destination<br>Addressing | Accombion I common                                    | Nonsegmented Mode            |        | Segmented Mode                                                                                                           |        |

|---------------------------|-------------------------------------------------------|------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------|--------|

| Mode                      | Assembler Language<br>Syntax                          | Instruction Format           | Cycles | Instruction Format                                                                                                       | Cycles |

| R:                        | BIT Rd, b<br>BITB Rbd, b                              | 10 10011 W Rd b              | 4      | 10 10011 W Rd b                                                                                                          | 4      |

| IR:                       | BIT @Rd <sup>1</sup> , b<br>BITB @Rd <sup>1</sup> , b | 00 10011 W Rd≠0 b            | 8      | 00 10011 W Rd≠0 b                                                                                                        | 8      |

| DA:                       | BIT address, b<br>BITB address, b                     | 01 10011 W 0000 b<br>address | 10     | SS 01 10011 W 0000 b<br>0 segment offset                                                                                 | 11     |

|                           |                                                       |                              |        | 01         10011         W         0000         b           1         segment         0000         0000           offset | 13     |

#### Example:

If register RH2 contains %B2 (10110010), the instruction BITB RH2, #0

will leave the Z flag set to 1.

# CALL Call

|         | <b>CALL</b> dst                                                                                   | dst: IR, DA, X                                                                                                     |

|---------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| ration: | Nonsegmented<br>$SP \leftarrow SP - 2$<br>$C \rightarrow SP \leftarrow PC$<br>$PC \leftarrow dst$ | Segmented<br>SP ← SP − 4<br>@SP ← PC<br>PC ← dst                                                                   |

|         | processor stack. The sta                                                                          | the program counter (PC) are pushed onto the top of the<br>ck pointer used is R15 in nonsegmented mode, or RR14 ir |

processor stack. The stack pointer used is R15 in nonsegmented mode, or RR14 in segmented mode. (The program counter value used is the address of the first instruction byte following the CALL instruction.) The specified destination address is then loaded into the PC and points to the first instruction of the called procedure. At the end of the procedure a RET instruction can be used to return to original program. RET pops the top of the processor stack back into the PC.

Flags:

Oper

No flags affected

| Destination<br>Addressing Assembler Language |               | Nonsegmented Mode              | ÷      | Segmented Mode                                                                                                                 |        |  |

|----------------------------------------------|---------------|--------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|--------|--|

| Mode                                         | Syntax        | Instruction Format             | Cycles | Instruction Format                                                                                                             | Cycles |  |

| IR:                                          | CALL @ Rd!    | 00 011111 Rd 0000              | 10     | 00 011111 Rd 0000                                                                                                              | 15     |  |

| DA:                                          | CALL address  | 01 011111 0000 0000<br>address | 12     | SS 01 011111 0000 0000<br>0 segment offset                                                                                     | 18     |  |

|                                              |               |                                |        | SL 01 011111 0000 0000<br>1 segment 0000 0000<br>offset                                                                        | 20     |  |

| Х:                                           | CALL addr(Rd) | 01 011111 Rd≠0 0000<br>address | 13     | SS 01 011111 Rs≠0 0000<br>0 segment offset                                                                                     | 18     |  |

|                                              |               |                                |        | 01         0111111         Rs≠0         0000           SL         1         segment         0000         0000           offset | 21     |  |

Example:

In nonsegmented mode, if the contents of the program counter are %1000 and the contents of the stack pointer (R15) are %3002, the instruction

CALL %2520

causes the stack pointer to be decremented to %3000, the value %1004 (the address following the CALL instruction with direct address mode specified) to be loaded into the word at location %3000, and the program counter to be loaded with the value %2520. The program counter now points to the address of the first instruction in the procedure to be executed.

# CALR Call Relative

|            | CALR dst                                                                                |                                                                                                                                                         | dst: RA                                                         |                                                                  |                                                                                     |                                                                           |                             |

|------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------|

| Operation: | Nonsegmentec<br>SP ← SP - 2<br>@SP ← PC<br>PC ← PC - (                                  |                                                                                                                                                         | t)                                                              | Segment<br>SP - SI<br>@SP - 1<br>PC - P                          | P – 4                                                                               | lacement)                                                                 |                             |

|            | processor stac<br>segmented. (T<br>byte following                                       | ontents of the prog<br>k. The stack point<br>he program count<br>the CALR instruc-<br>e PC and points to                                                | er used is<br>er value<br>tion.) Th                             | s R15 if no<br>used is th<br>e destinat                          | onsegmented,<br>e address of t<br>ion address is                                    | or RR14 if<br>he first instru<br>calculated a                             | iction                      |

|            |                                                                                         | the procedure a R<br>RET pops the top                                                                                                                   |                                                                 |                                                                  |                                                                                     |                                                                           | riginal                     |

|            | instruction, the<br>destination ad<br>+2047. Thus,<br>from the start<br>is not affected | n address is calcu<br>en subtracting this<br>dress. The displac<br>the destination ad<br>of the CALR instru-<br>. The assembler ar<br>e PC value of the | s value fra<br>ement is<br>dress mus<br>uction. In<br>utomatica | om the cu<br>a 12-bit s<br>st be in th<br>segment<br>illy calcul | rrent value of<br>igned value ir<br>e range –409<br>ed mode, the<br>ates the displa | the PC to de<br>the range -<br>12 to +4098 b<br>PC segment<br>accement by | -2048 to<br>oytes<br>number |

| Flags:     | No flags affect                                                                         | ed                                                                                                                                                      |                                                                 |                                                                  |                                                                                     |                                                                           |                             |

|            |                                                                                         |                                                                                                                                                         |                                                                 |                                                                  | -                                                                                   |                                                                           |                             |

| Destination<br>Addressing                    |              | Nonsegmented Mode  |        | Segmented Mode     |        |

|----------------------------------------------|--------------|--------------------|--------|--------------------|--------|

| Addressing Assembler Language<br>Mode Syntax |              | Instruction Format | Cycles | Instruction Format | Cycles |

| RA:                                          | CALR address | 1101 displacement  | 10     | 1101 displacement  | 15     |

Example:

In nonsegmented mode, if the contents of the program counter are %1000 and the contents of the stack pointer (R15) are %3002, the instruction

CALR PROC

causes the stack pointer to be decremented to %3000, the value %1004 (the address following the CALR instruction) to be loaded into the word location %3000, and the program counter to be loaded with the address of the first instruction in procedure PROC.

# CLR Clear

CLR dst dst: R, IR, DA, X CLRB **Operation:** dst 🗕 0 The destination is cleared to zero. Flags: No flags affected. Segmented Mode Destination **Nonsegmented Mode** Addressing Assembler Language Mode Syntax Instruction Format Cycles Instruction Format Cycles R: CLR Rd 10 00110 W Rd ≠ 0 1000 7 10 00110 W Rd ≠ 0 1000 7 CLRB Rbd IR: CLR @Rd1 00 00110 W Rd ≠ 0 1000 0 0 0 0 1 1 0 W Rd ≠ 0 1 0 0 0 8 8 CLRB @Rd1 DA: CLR address 01 00110 W 0000 1000 01 00110 W 0000 1000 CLBB address SS 11 12 address seament offset 0 01 001 10 W 0000 1000 0000 0000 14 SL 1 segment offset X: CLR addr(Rd) 01 00110 W Rd≠0 1000 00110 W Rd≠0 1000 0 1 CLRB addr(Rd) 12 12 SS address segment offset 0100110W Rd≠0 1000 SL 0000 0000 15 1 segment offset

Example:

If the word at location %ABBA contains 13, the statement CLR %ABBA

will leave the value 0 in the word at location %ABBA.

# **COM** Complement

|            | COM dst<br>COMB                                                | dst: R, IR, DA, X                                                                                                    |